本文主要介(jiè)绍数(shù)字电路(lù)基础知(zhī)识(shí),用最简洁的内(nèi)容(róng)介(jiè)绍(shào)最核心(xīn)的(de)知识(shí)。

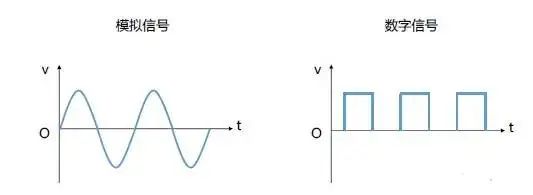

1、数字(zì)电路是什么?数字电路(lù)是利用电源电压的高电平和低电平分别表示(shì)1和0,进而(ér)实现(xiàn)信息的表达(dá)。模拟信号:随时间连续(xù)变化的信号。处理(lǐ)模拟信(xìn)号的电路就是模拟电路。数(shù)字信号:随时间不连续变(biàn)化的信号(hào),离散变化(huà)。处理(lǐ)数字信号(hào)的电路就是数字电路。

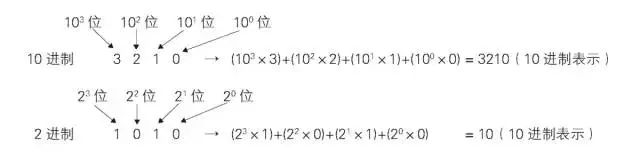

2、数值表达我们常用的数值表达方式是十进制,但在数(shù)字电路中采用的是二进制,如下图所(suǒ)示(shì):

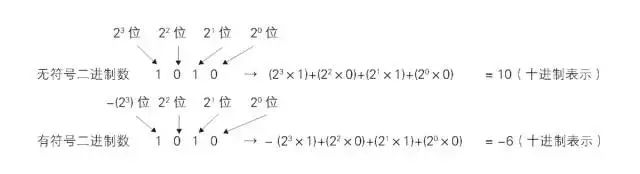

有符号二进制:

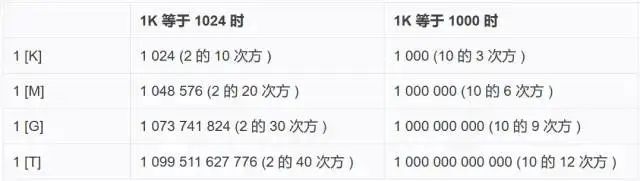

3、比特和(hé)字节比特:二进制中的一个数字位称为 binary digit,用bit表(biǎo)示(shì),常简(jiǎn)写为“b”。字节:1字节(jiē)等于(yú)8比特,用(yòng)byte表示,常简写为(wéi)“B”。4、1K 字节理解的差异K、M、G、T 是表(biǎo)示大数据量时常用的单位。1K 的大小(xiǎo)有(yǒu) 1000(10 的(de) 3 次方)和 1024(2 的 10 次方)两种计数方法。通常,衡量计算机(jī)内存和网络数据包大小时,1K 相(xiàng)当于 1024 比特。而在硬(yìng)盘等存储器的(de)标签上记述的尺寸或(huò)物理学(xué)中的 1K 相当于 1000。

5、反(fǎn)码与补码反(fǎn)码 = 原码(mǎ)所有bit位取反补码 = 反码+1比(bǐ)如原码=0101,则(zé)反(fǎn)码(mǎ)=1010,补(bǔ)码=1011

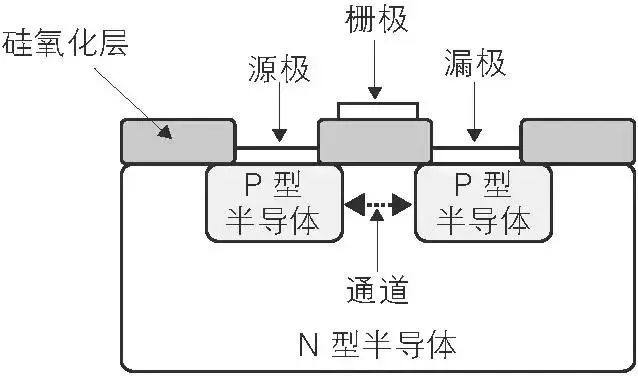

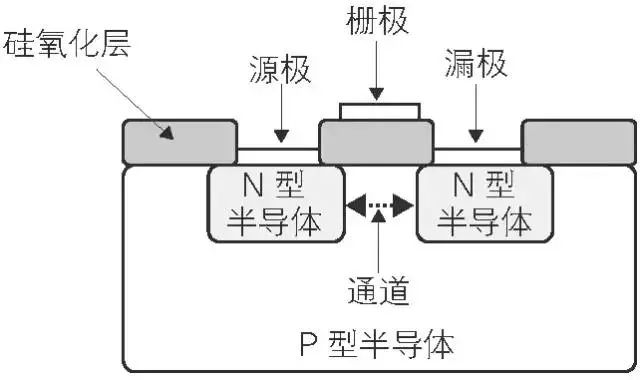

6、MOSFET的结构目(mù)前数字电路(lù)基本上都是由 MOSFET 场效应管(guǎn)构成的。MOSFET 是一种(zhǒng)在施加电压后(hòu)可以(yǐ)像开关(guān)一样工作的半导(dǎo)体器件。MOSFET 有 P 型 MOSFET 和 N 型 MOSFET 两种。

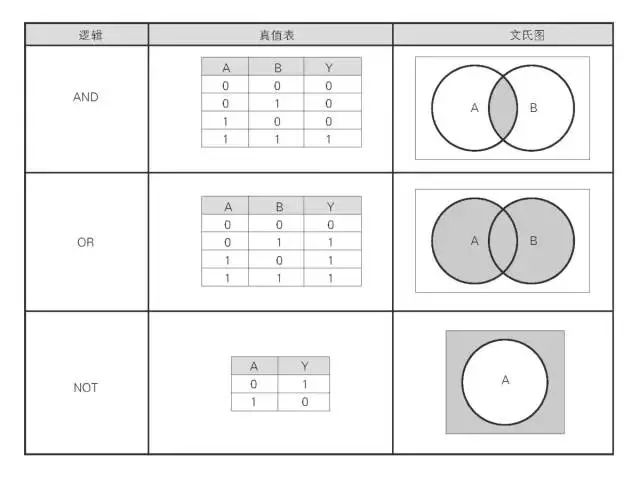

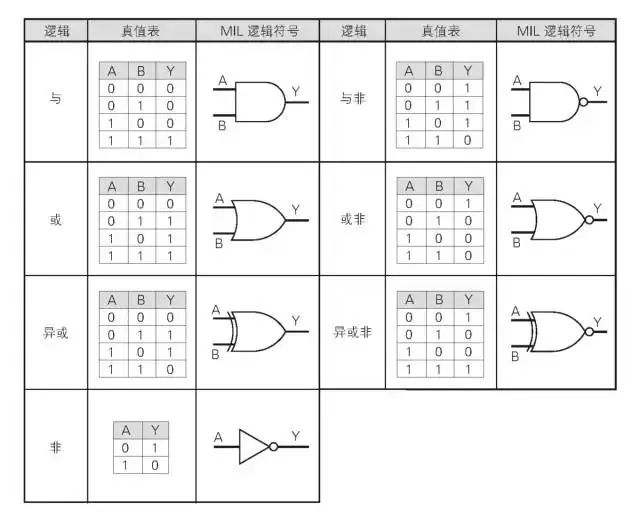

7、逻辑运算与基本逻辑门电路(lù)(1)逻辑运算(suàn)使用 AND(逻(luó)辑与)、OR(逻辑或)、NOT(逻辑非)三种基本运算(suàn)组合来实现(xiàn)各种运算。

(2)CMOS 基本逻辑门电路

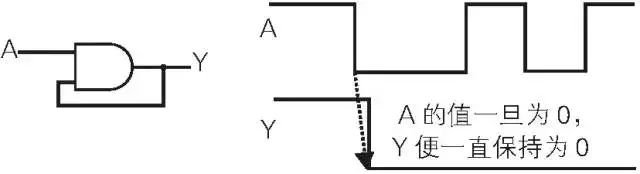

8、存储元件锁存器(Latch)就(jiù)是一种存储元件,具(jù)有像闩(shuān)锁(suǒ)一样锁住(zhù)并(bìng)维持数据的特性,通(tōng)过组合基本的逻辑门可以实现(xiàn)。

(1)最简单的锁存器由一个2输入的AND门组成(chéng),将一路(lù)输入与输(shū)出连接形成回路。

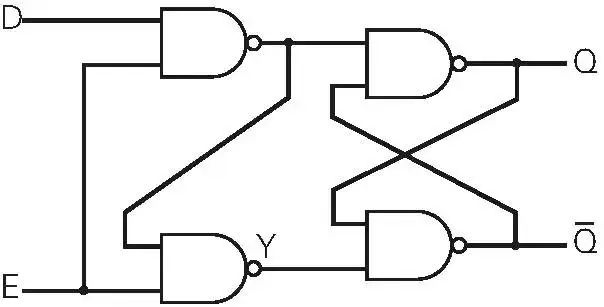

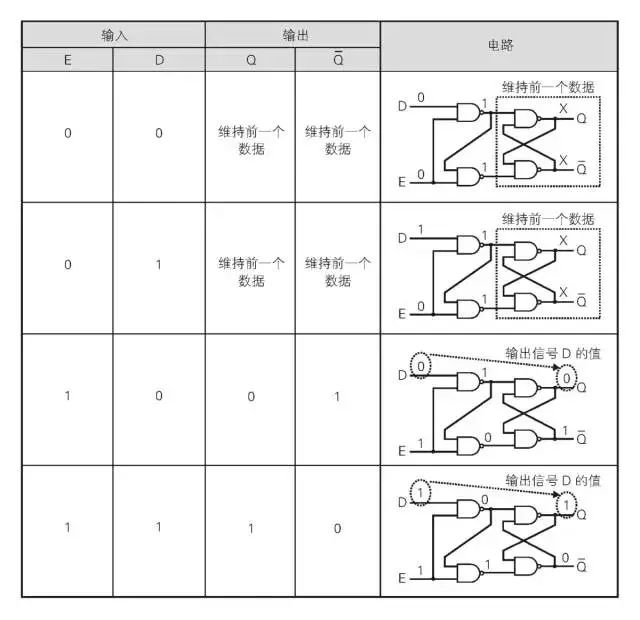

(2)D锁存(cún)器(Data Latch,D-Latch,数据锁存器)由4个NAND组成,输(shū)入信号有D(DATA)和E(ENABLE),输出信号(hào)有(yǒu)Q和/Q。工作(zuò)逻辑:E 为 0 时保持前一个数据(jù),E 为 1 时将输(shū)入 D 的数据(jù)输(shū)出到 Q。E为1时输入(rù)的 D 直接(jiē)通过 Q 输(shū)出。D锁(suǒ)存器构成以及电(diàn)路组成如下:

真值表:

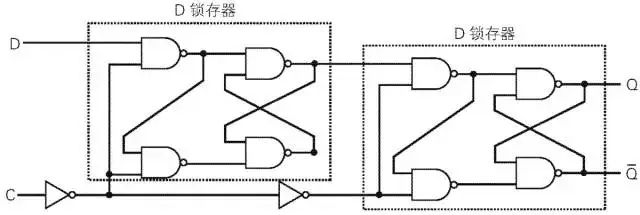

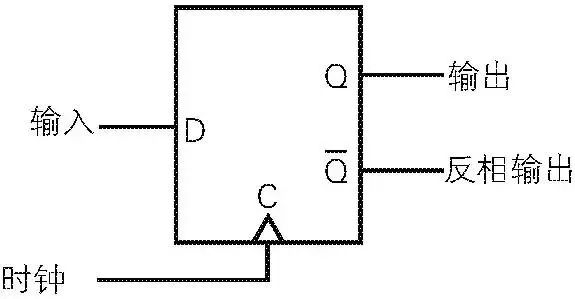

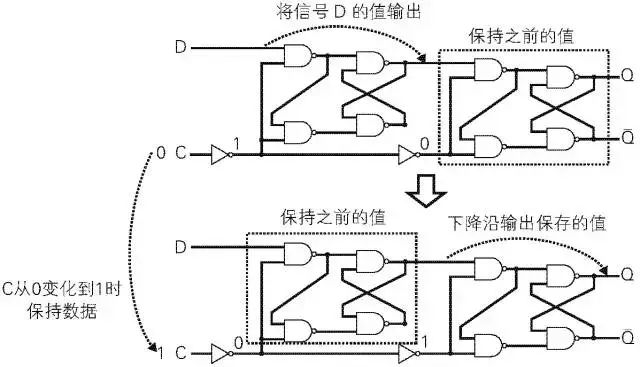

(3)D触发(fā)器D 锁存器和 NOT 门组合(hé),可以(yǐ)实现依据时钟信号(hào)同步并保(bǎo)存数据的(de) D 触发器。D 触发器有 D(Data) 和(hé) C(Clock) 两个输入信号,Q 和

两个(gè)输出信号。D触发器电路组合如下图所示。

D触发器的电路符(fú)号:

工作逻(luó)辑:当(dāng) D 触 发器的 C 为 0 时,前端 D 锁存器输出信号 D 的值,后端 D 锁存器(qì)保持之前的数据。当 C 为 1 时,前(qián)端 D 锁存器保持之前的数据,后端 D 锁存器将前(qián)端 D 锁存器保持的(de)数据(jù)直接通过 Q 输出。

D触(chù)发器由于原理和构造简单,广(guǎng)泛应用于同步(bù)电路。

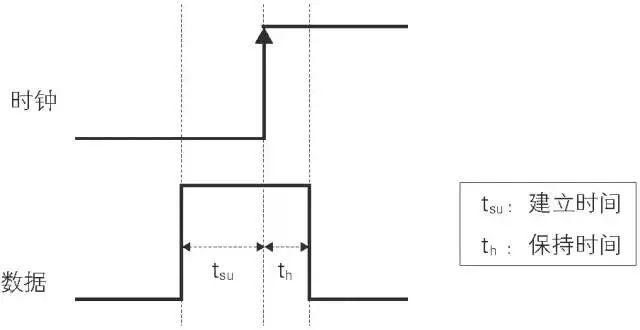

扩展(zhǎn)知识:《建立(lì)时间与保持(chí)时间》D 触(chù)发器(qì)是由(yóu)时钟信号的边沿(yán)来(lái)触(chù)发数据(jù)的存储动作的。因此,需要(yào)在时钟沿前(qián)后一(yī)段时间内将(jiāng)输入信号稳定下(xià)来。如果(guǒ)在时钟(zhōng)变化时(shí)输入信号也在变化,很可能无法正确存储数(shù)据。因此,为了让 D 触(chù)发器(qì)正确存储数(shù)据,需要有建(jiàn)立时间(setup time)和保持时间(hold time)两(liǎng)个基本条件。建立时间是在时钟变化前必须稳定(dìng)输入信号的时(shí)间,而(ér)保持时间是时钟变化后(hòu)必(bì)须稳定输入信号(hào)的(de)时(shí)间。同时遵守建立时间和保持时间,就可(kě)以让 D 触发器(qì)正(zhèng)确的(de)存储数据。具体的时序图(tú)如下所(suǒ)示:

9、组合逻辑(jí)电路和时序逻辑电路(lù)数字电(diàn)路可以分为(wéi)组逻(luó)辑合电路和(hé)时序逻辑电路(lù)两种。

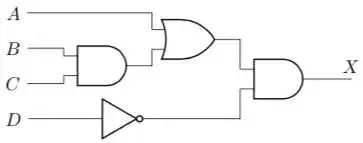

(1)组合逻辑电路组合逻辑电路是(shì)指输出值仅由输入信号的状(zhuàng)态决定的电路,不依赖于过去的输入。从电路组成上来看,只包含门电路,不包含(hán)存储元件。比如下图所(suǒ)示就是一(yī)个组合逻辑电路。

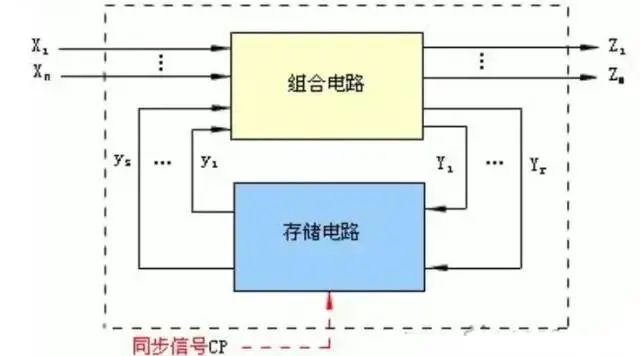

(2)时序逻辑电路时序逻辑电(diàn)路(lù)是指输(shū)出值同时依赖于现在和过(guò)去输入信号的逻(luó)辑电(diàn)路(lù)。从电路组成上来(lái)看,时序逻辑电路等于(yú)组合逻(luó)辑电(diàn)路(lù)+存(cún)储(chǔ)电路。从工作逻辑上来看,输出状态必(bì)须反馈到(dào)输入端(duān),与输入信号共同决(jué)定组合逻辑的输出。

客服QQ1:63355785 客服QQ2:61303373 客服QQ3:67399965 客服QQ4:2656068273 产品分类地(dì)图

版权(quán)所有:保定市乐动网页版和禾邦电子有限公司(sī) 保定市禾(hé)邦电子有限公司营(yíng)业执照

关键字:保定电(diàn)子元器件(jiàn) 保(bǎo)定电子(zǐ)元件 电子元器件(jiàn) 电子元件